-

芯片產業鏈條深度分析!發布時間:2021.06.18

一、半導體是電子產品的核心,信息產業的基石

從晶體管誕生

, 計算機的基礎是1和0

, , , , , 。 , , , 。

通過在半導體材料里摻入不同元素

, 。 , , , 。

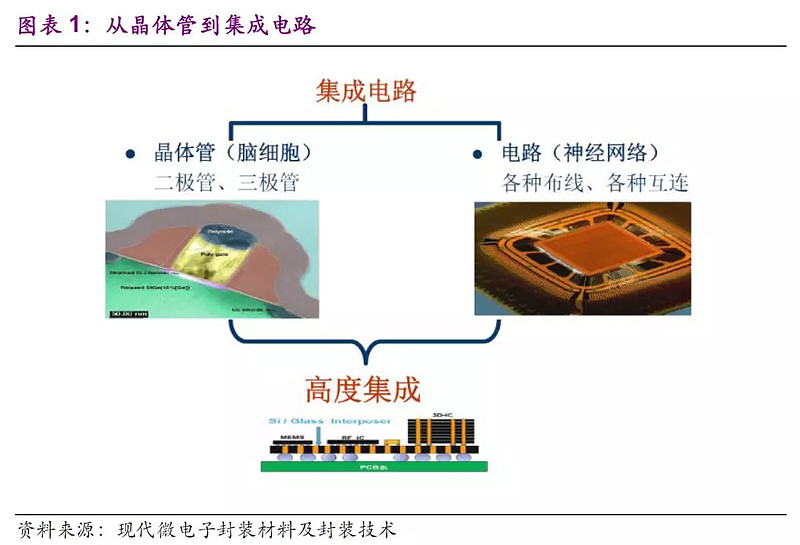

把一個電路中所需的晶體管

、 、 , , , , , 。 , 、 、 。

集成電路發明者為杰克

· 基爾比( ( ) ) · 諾伊思( ( ) ) 。 。

1965年

, · 摩爾( ) , 。 , · 諾伊斯和戈登· 摩爾從仙童( ) , , , “ 集成電子設備( ) ” 的縮寫。

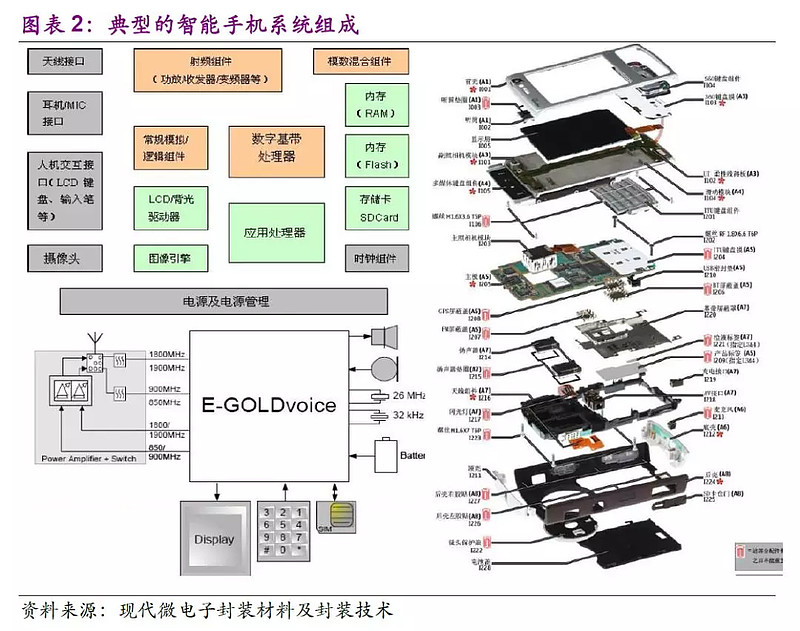

電子產品的核心

, 以智能手機為例

, 、 、 , ; 通常所說的2G或者4G運行內存RAM為DRAM, ; 音視頻多媒體芯片為模擬IC。 。

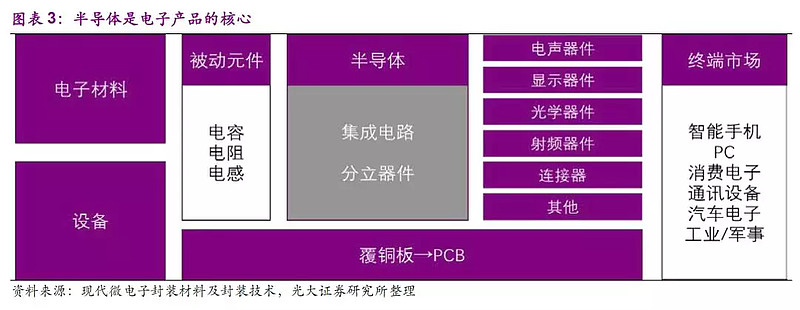

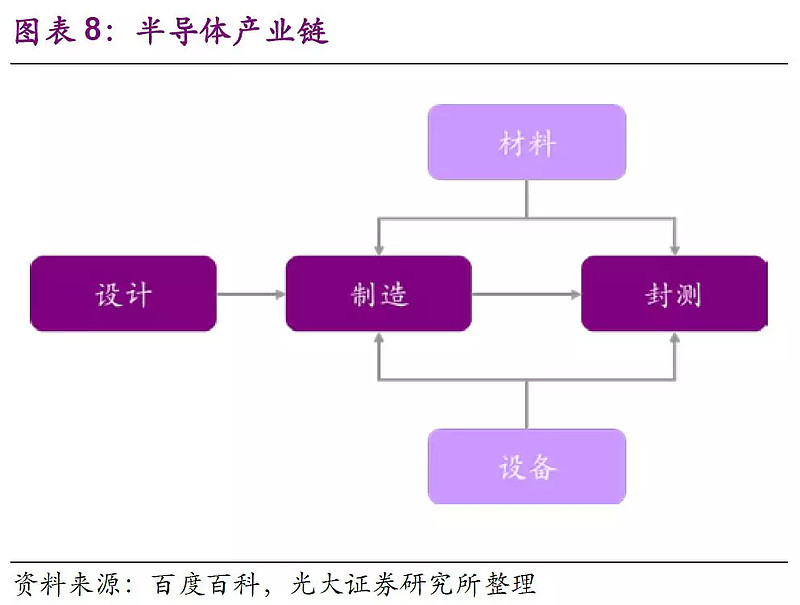

半導體位于電子行業的中游

, 。 , 、 , , 。

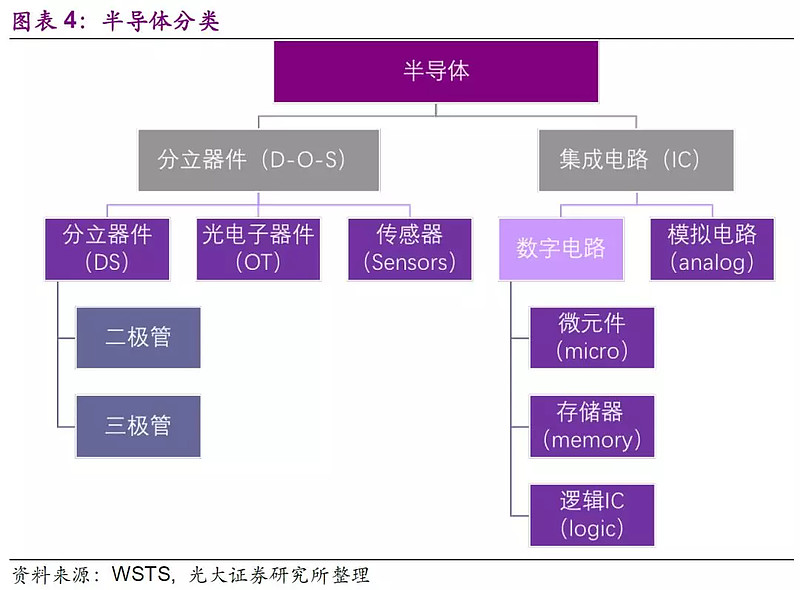

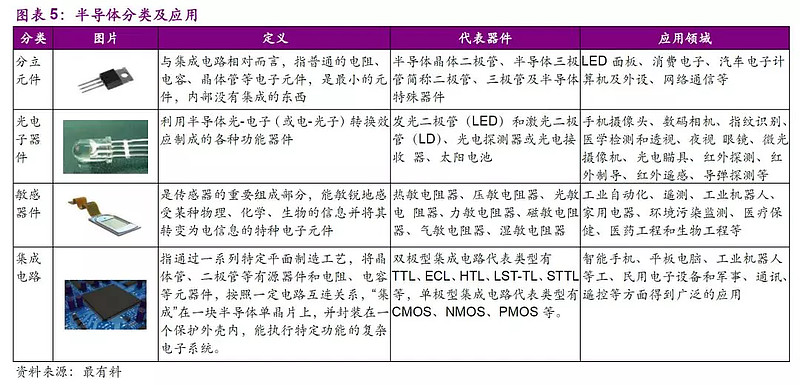

半導體主要分為集成電路和半導體分立器件

。 、 。

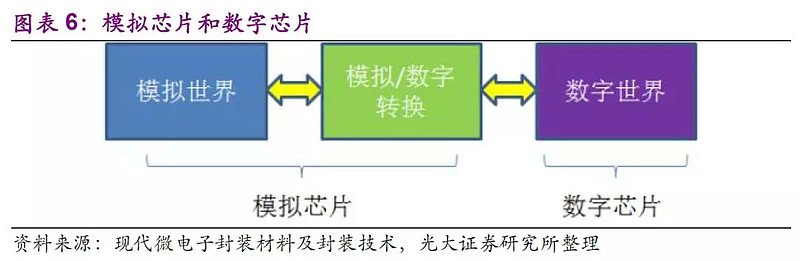

集成電路可分為數字電路

、 。 : 圖像, , , , 。 , 。 , , , , , 。 、 。 ( 、 、 、 ) , ( 、 、 ) ( 、 ) 。

二、 、 、

簡單的講

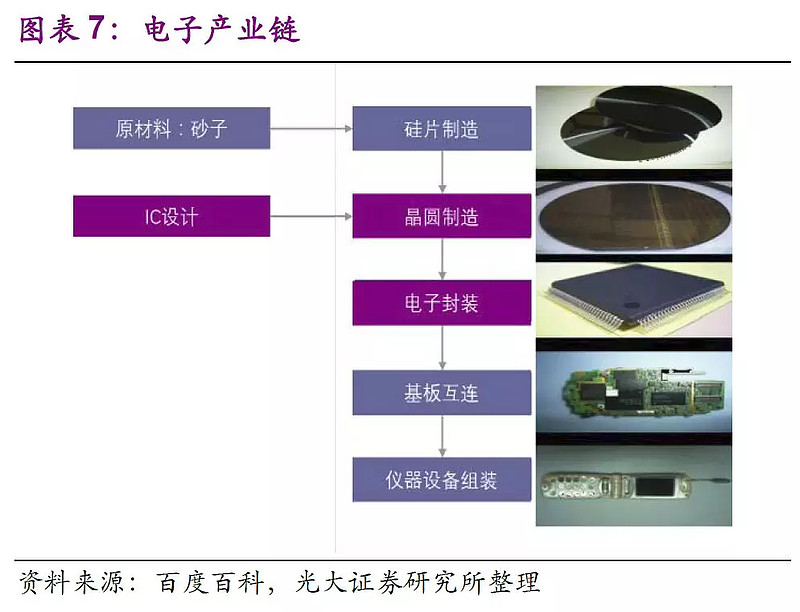

, : 原材料砂子-硅片制造-晶圓制造-封裝測試-基板互聯-儀器設備組裝。 、 、 。

集成電路產業主要有以下特征

: 制造工序多、 、 、 。

生產工序多

: 核心產業鏈流程可以簡單描述為: IC設計公司根據下游戶( ) , , 。 , , 。

具體來說

, :

>IC設計

: 根據客戶要求設計芯片IC設計可分成幾個步驟

, : 規格制定→邏輯設計→電路布局→布局后模擬→光罩制作。 : 品牌廠或白牌廠的工程師和IC設計工程師接觸, ; 邏輯設計: IC設計工程師完成邏輯設計圖; 電路布局: 將邏輯設計圖轉化成電路圖; 布局后模擬: 經由軟件測試, ; 光罩制作: 將電路制作成一片片的光罩, 。

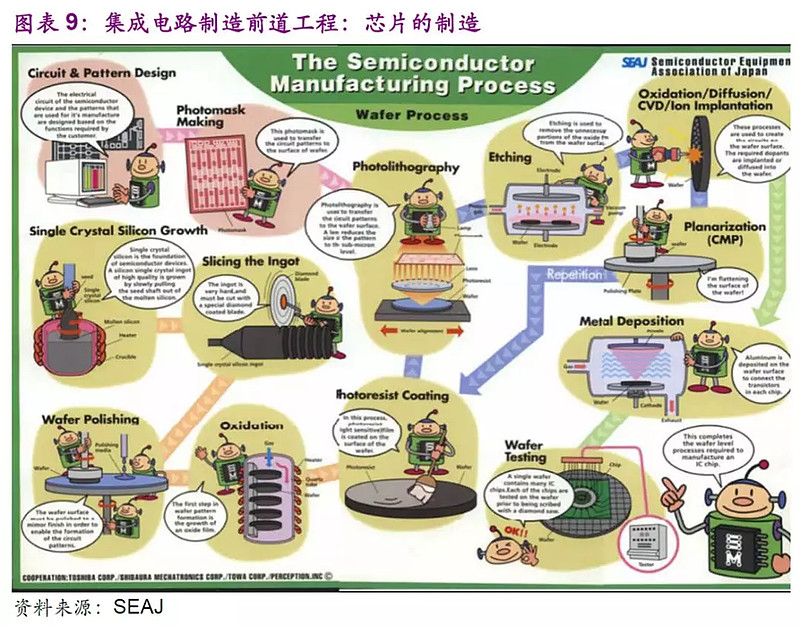

>IC制造

: 將光罩上的電路圖轉移到晶圓上IC制造的流程較為復雜

, : 薄膜→光刻→顯影→蝕刻→光阻去除。 : 在晶圓片表面上生長數層材質不同, ; 光刻: 將掩膜板上的圖形復制到硅片上。 , ;

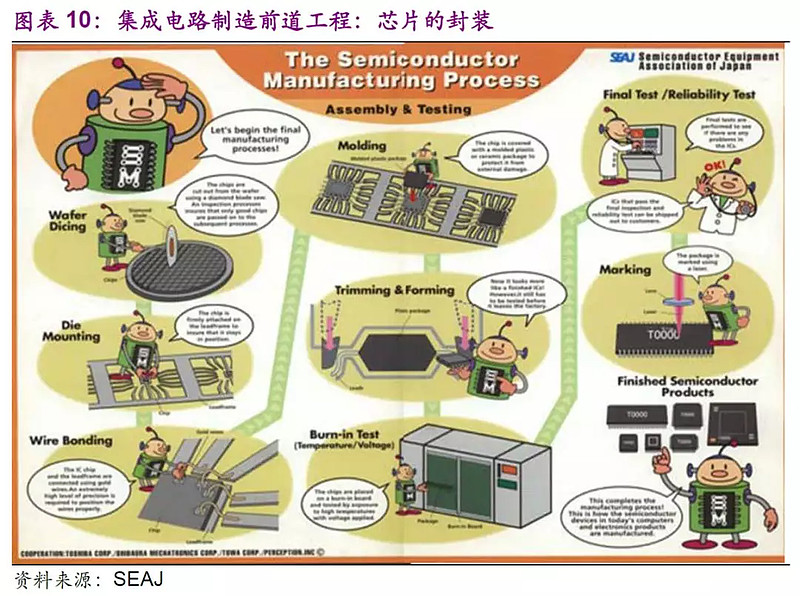

>IC封測

: 封裝和測試封裝的流程大致如下

: 切割→黏貼→切割焊接→模封。 : 將IC制造公司生產的晶圓切割成長方形的IC; 黏貼: 把IC黏貼到PCB上; 焊接: 將IC的接腳焊接到PCB上, ; 模封: 將接腳模封起來;

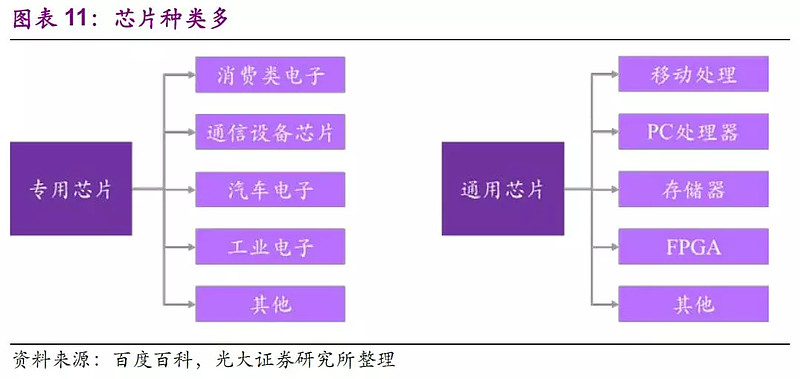

產品種類多

。 , 。 、 、 , 。 、 , 、 。 , 。 , , ; 汽車電子需要輔助駕駛系統芯片、 , 。

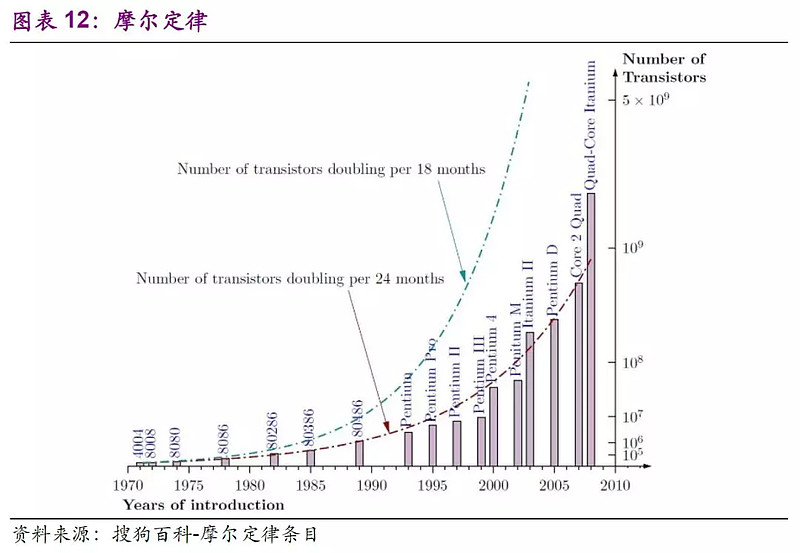

技術更新換代快

。 : 當價格不變時, , , , 。

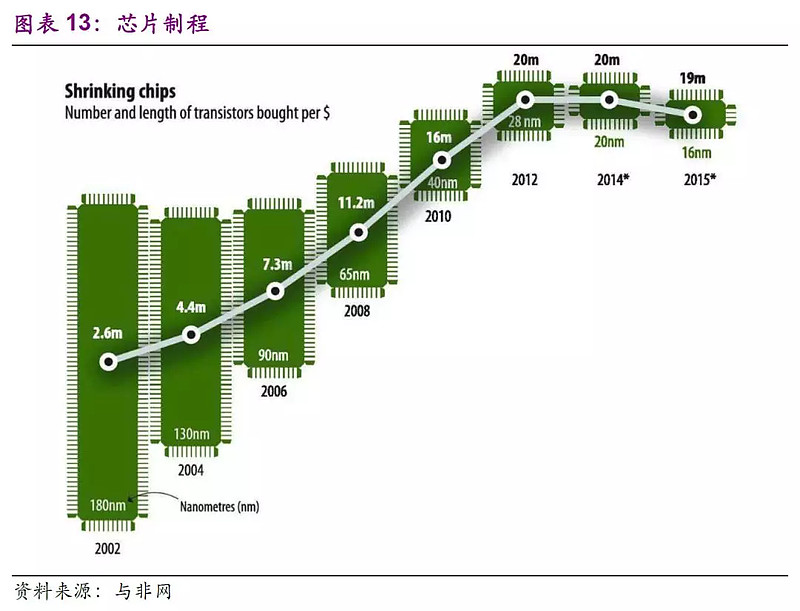

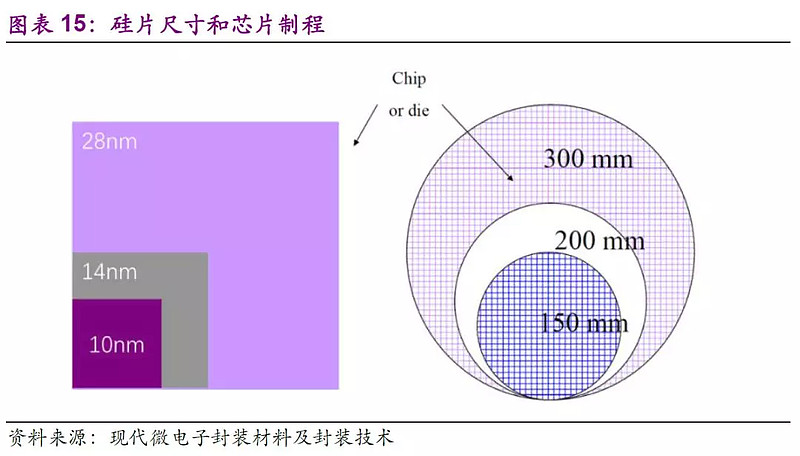

芯片的制程就是用來表征集成電路尺寸的大小的一個參數

, , 、 、 、 、 、 、 、 、 、 、 、 、 , 、 、 。 , 。

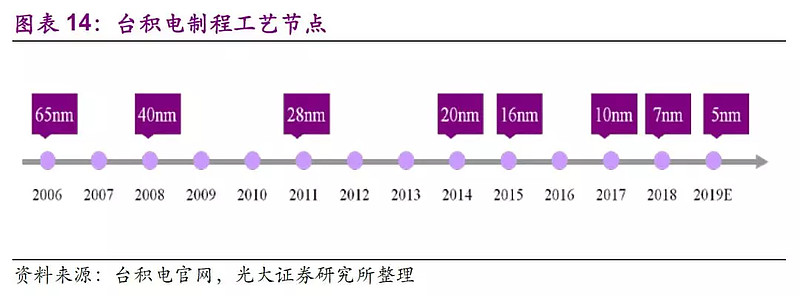

以臺積電為例

, 。 , , 。 。 , 。

除了制程

, , 。 ( ) 、 ( ) 、 ( ) , , 。 , , 。

投資大風險高

。 《 》 , , , , 。 , 。 , 。 , , , , 。

集成電路設計存在技術和市場兩方面的不確定性

。 , 。 , 。 , , , 。 , 。 , , 。

作者:慧博

鏈接:https://xueqiu.com/3966435964/127571664

來源:雪球

著作權歸作者所有。商業轉載請聯系作者獲得授權,非商業轉載請注明出處。

風險提示:本文所提到的觀點僅代表個人的意見,所涉及標的不作推薦,據此買賣,風險自負。